KianV RV32IMA

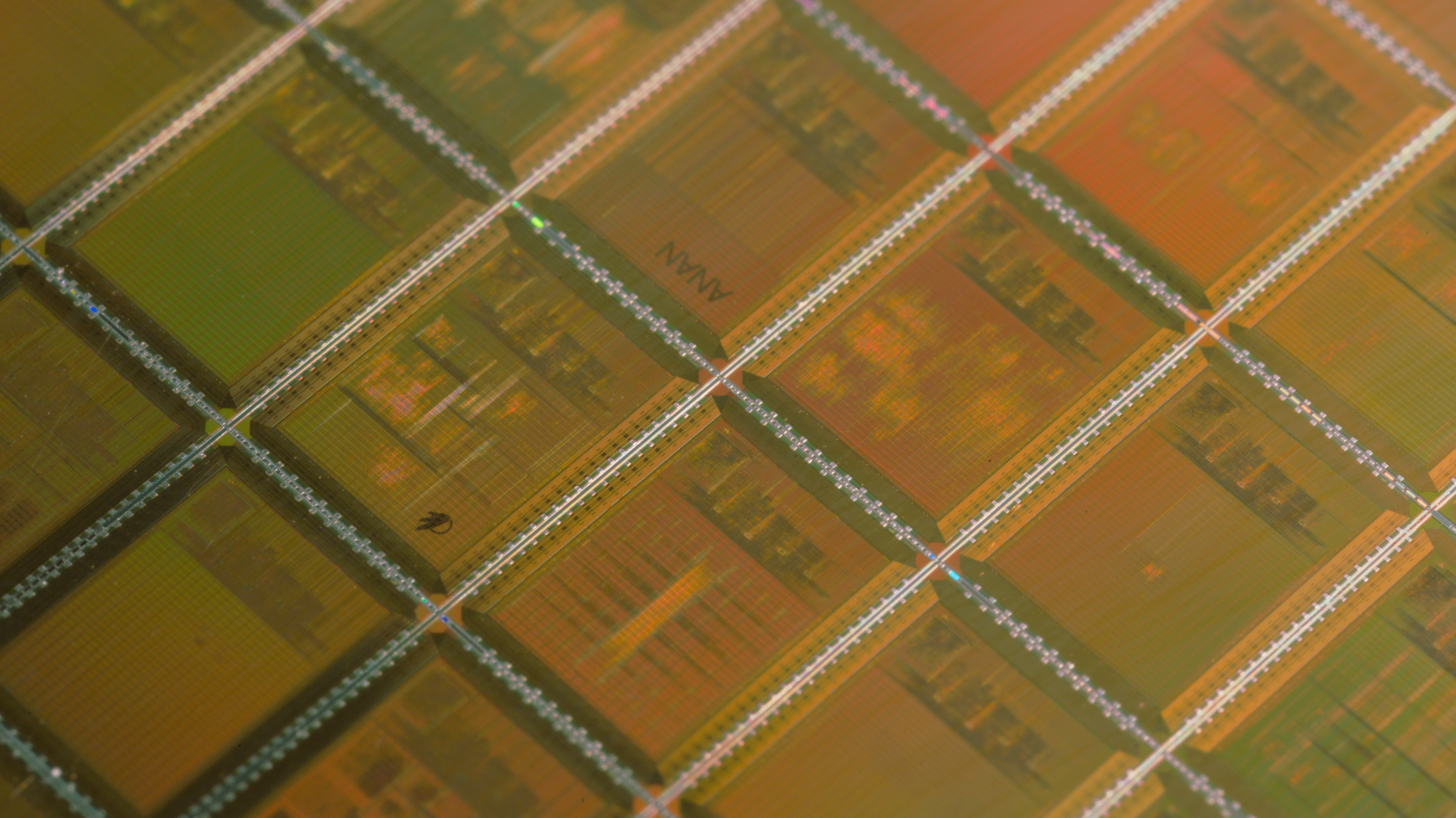

RISC-V SoC running Linux on GF180MCU

GF180MCU process details and what you can build

Getting from your design to manufactured silicon is a collaborative process. You handle the design and submission, we take care of fabrication and delivery.

What you need to do to get your chip manufactured

Join the campaign and secure your manufacturing slot

Create your chip using the open GF180MCU PDK and your preferred tools

Complete DRC/LVS/ERC checks and follow our design guidelines

Provide your tape-in files following our submission checklist

After you complete your design and submission, wafer.space handles all the manufacturing logistics for you.

What wafer.space takes care of for you

We process your design in our pooled multi-project wafer run

We dice the wafers and prepare your parts for shipment

We ship your ~1,000 bare dies and any optional packaging

3 Sizes

Full, Half Width, Half Height

5 Layers

Full routing capability

1,000 dies

Per manufacturing slot

MIM & MOS

Metal-insulator-metal and MOS capacitors available

Poly & High-Res

Multiple resistor types

Silicon currently in fabrication — expected delivery late April 2026

1×1 slot

1×1 slot

1×1 slot

1×1 slot

1×1 slot

1×1 slot

1×1 slot

1×1 slot

1×1 slot

1×1 slot

Hard upper bounds — if you packed cells edge-to-edge with zero routing overhead

Flip-Flop (FF_1)

per mm² theoretical max

Buffer (BUF_4)

per mm² theoretical max

3-input AND (AND3_2)

per mm² theoretical max

Typical Range

logic cells/mm² for most digital designs

across 24 designs

| Design | Library | Core SC/mm² | % of max | Logic Cells | SRAM |

|---|---|---|---|---|---|

| Cloneless1 | 7t-5V | 22k | 44% | 316k | 0 |

| Tiny Tapeout (52 sub-designs) | mixed | 14k | 29% | 204k | 0 |

| FABulous FPGA | 7t-5V | 14k | 29% | 204k | 12 |

| Chess Move Gen. | 9t-5V | 10k | 25% | 145k | 0 |

| FazyRV Hachure | 7t-5V | 7k | 14% | 101k | 40 |

| KianV RISC-V | 9t-5V | 6k | 16% | 89k | 42 |

| Racquet 23-core | 7t-5V | 5k | 11% | 78k | 46 |

Data from the Run 1 Density Report. Logic cell counts exclude infrastructure cells (fillers, taps, antenna diodes). “% of max” compares against buf theoretical max for each library (50k for 7-track, 40k for 9-track).

| Cell Type | 1×1 Slot |

New! 0.5×1 Slot |

New! 1×0.5 Slot |

|---|---|---|---|

| Flip-Flop (FF_1) | ~185,014 | ~63,867 | ~71,886 |

| Buffer (BUF_4) | ~393,156 | ~135,718 | ~152,759 |

| 3-input AND (AND3_2) | ~508,790 | ~175,635 | ~197,688 |

Theoretical maximums with zero routing overhead. Run 1 designs typically achieved 10–44% of these values.

| SRAM Type | Voltage | 1×1 Slot | 0.5×1 Slot | 1×0.5 Slot |

|---|---|---|---|---|

| GF 5V sram512x8 | 5V | 40 kilobytes (80 blocks) | 20 kilobytes (40 blocks) | 20 kilobytes (40 blocks) |

| GF 5V sram256x8 | 5V | 28 kilobytes (112 blocks) | 14 kilobytes (56 blocks) | 14 kilobytes (56 blocks) |

| 3.3V sram1024x8 | 3.3V | 108 kilobytes (108 blocks) | 54 kilobytes (54 blocks) | 48 kilobytes (48 blocks) |

| 3.3V sram512x8 | 3.3V | 90 kilobytes (180 blocks) | 45 kilobytes (90 blocks) | 42 kilobytes (84 blocks) |

| 3.3V sram256x8 | 3.3V | 66 kilobytes (264 blocks) | 33 kilobytes (132 blocks) | 33 kilobytes (132 blocks) |

Block counts use die area minus seal ring (26µm each side). Run 1’s most SRAM-heavy design (RISCBoy-180) used 60 blocks in a full slot.

Theoretical numbers use core area (with default pad ring). Using your own pad ring or no pad ring increases available area.

Real designs achieve 10–44% of theoretical max due to routing overhead, infrastructure cells (~75% of instances), power planning, and clock distribution.

3.3V SRAM blocks from Tim Edwards and Tholin, introduced in Run 1.

Full analysis: Run 1 Standard Cell & SRAM Density Report.

Professional design services are available from independent consultants experienced with the GF180MCU process. Whether you need a full custom design, help with verification, or guidance on your first tapeout, experts are ready to assist.