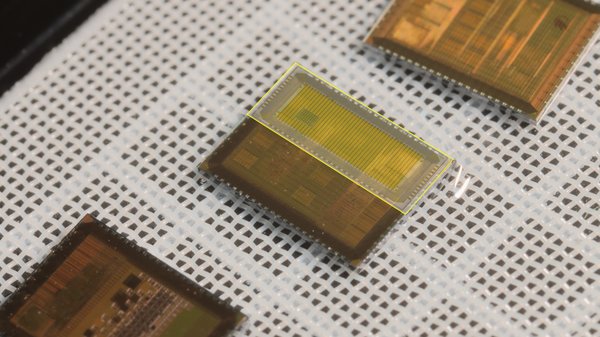

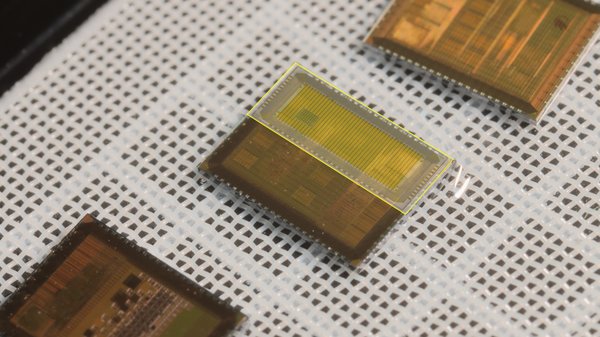

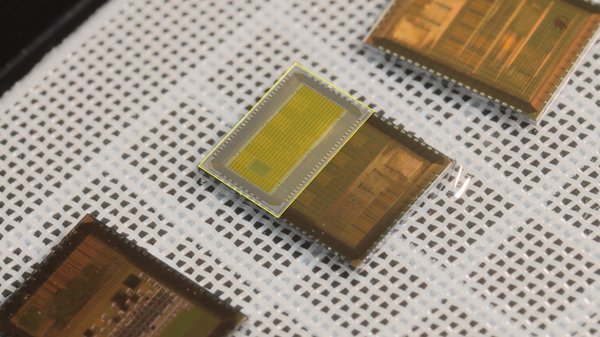

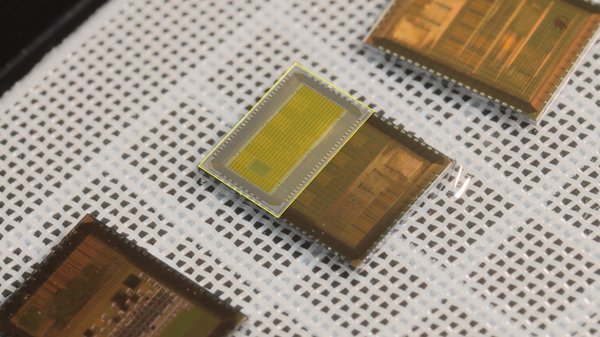

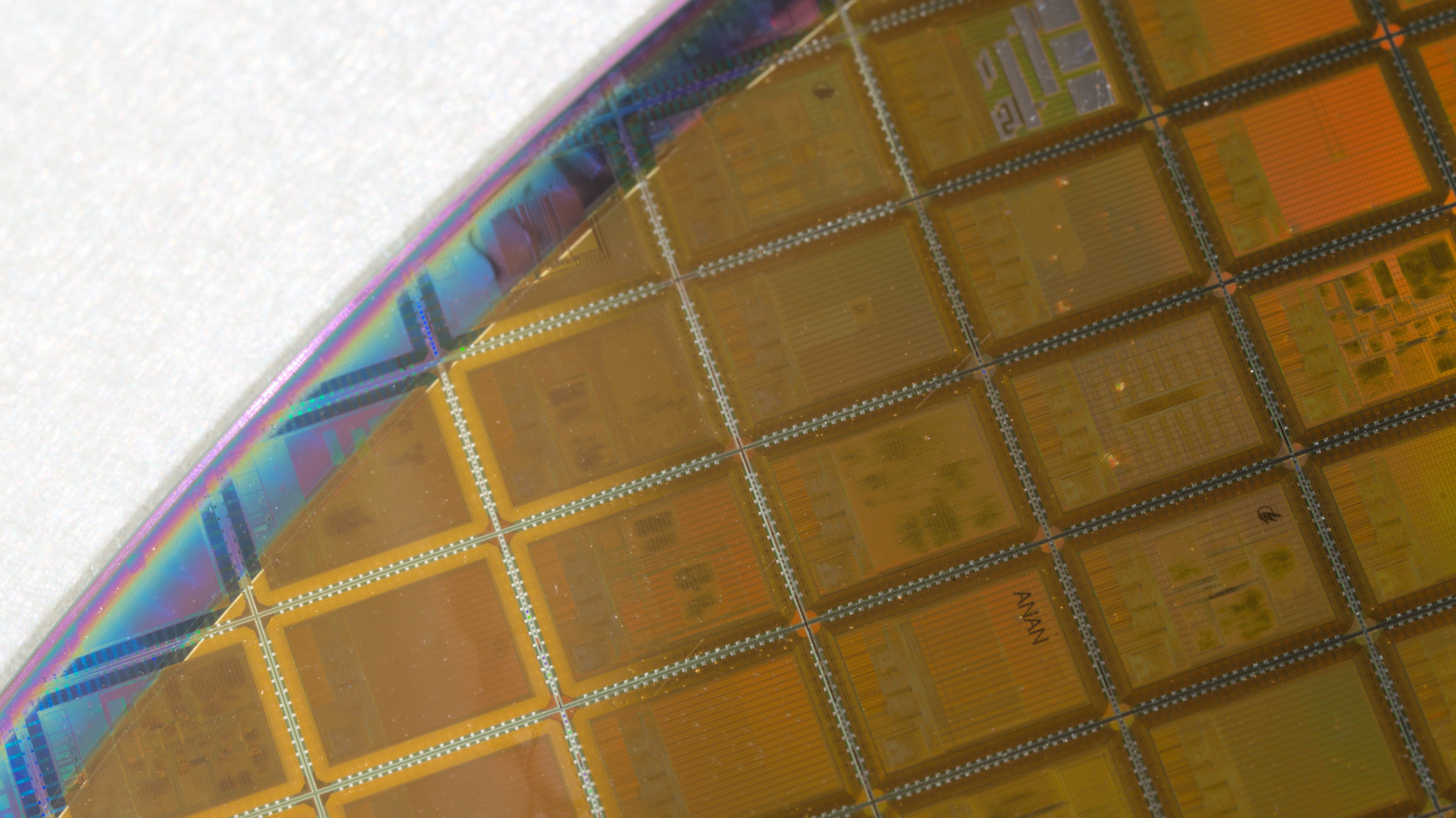

KianV RV32IMA

RISC-V SoC running Linux on GF180MCU

New half-width (0.5×1 slot) and half-height (1×0.5 slot) options — 1,000 dies for $4,000 with Early Bird pricing.

See Half Slot PricingLock in early bird pricing for GF180MCU Run 2

days

hours

minutes

seconds

Final deadline to purchase a slot and submit your GDS

days

hours

minutes

seconds

| Milestone | Date | Description |

|---|---|---|

| Campaign Opens | 1 March 2026 | Run 2 slots available for purchase on Crowd Supply |

| Early Bird Deadline | 30 April 2026 @ 11:59 PM AoE | Last day to purchase at early bird pricing |

| Purchase & Submission Deadline | 30 June 2026 @ 11:59 PM AoE | Final deadline to purchase slots and submit GDS files |

| Parts Shipped | Early Q4 2026 | Bare dies and packaged parts shipped to customers |

Professional design services are available from independent consultants experienced with the GF180MCU process. Whether you need a full custom design, help with verification, or guidance on your first tapeout, experts are ready to assist.

| Feature | 1×1 Slot |

New! 0.5×1 Slot |

New! 1×0.5 Slot |

|---|---|---|---|

| Die Size | 3.93 × 5.12 mm | 1.94 × 5.12 mm | 3.93 × 2.53 mm |

| Die Area | 20.12 mm² | 9.93 mm² | 9.94 mm² |

| Usable Silicon† | 19.65 mm² | 9.57 mm² | 9.61 mm² |

| Core Area* | 12.92 mm² | 4.46 mm² | 5.02 mm² |

| Default I/O Pads† | 56 | 56 | 56 |

| Max I/O Pads‡ | 168 | 122 | 108 |

| Early Bird Price | $7,000 | $4,000 | $4,000 |

| Standard Price | $7,500 | $4,500 | $4,500 |

| Per Die (Early Bird) | $7.00 | $4.00 | $4.00 |

†Default pad ring I/O count. The default pad ring is only required if you purchase the Chip on Board packaging add-on.

‡Maximum I/O with a custom pad ring from the LibreLane pad ring generator. You are free to use any pad ring configuration — or no pad ring at all.

*Usable silicon = die area minus seal ring (~26µm each side). Available with a custom pad ring or no pad ring.

*Core area = area inside the default pad ring.

USD $4,000

USD $4,500

The half-width (0.5×1) slot delivers a tall, narrow die — ideal for I/O-heavy designs where signals concentrate along the long edges. Perfect for medium-complexity digital or mixed-signal projects, at just over half the cost of a full slot.

USD $4,000

USD $4,500

The half-height (1×0.5) slot gives you a wide, short die — ideal for designs that benefit from a wider core. Offers slightly more core area than the half-width slot at the same price.

USD $7,000

USD $7,500

The full-size slot gives you the largest die area and maximum I/O count. Ideal for complex SoCs, full mixed-signal designs, or projects that need the most routing and core area.

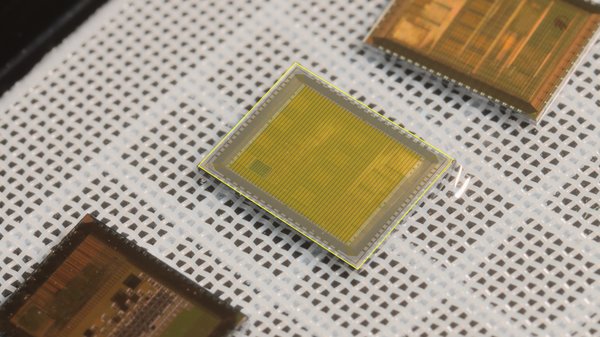

Receive your dies wire-bonded onto small PCBs, ready for testing and integration.

Add-on to any slot purchase. Requires the default pad ring.

Add to Order

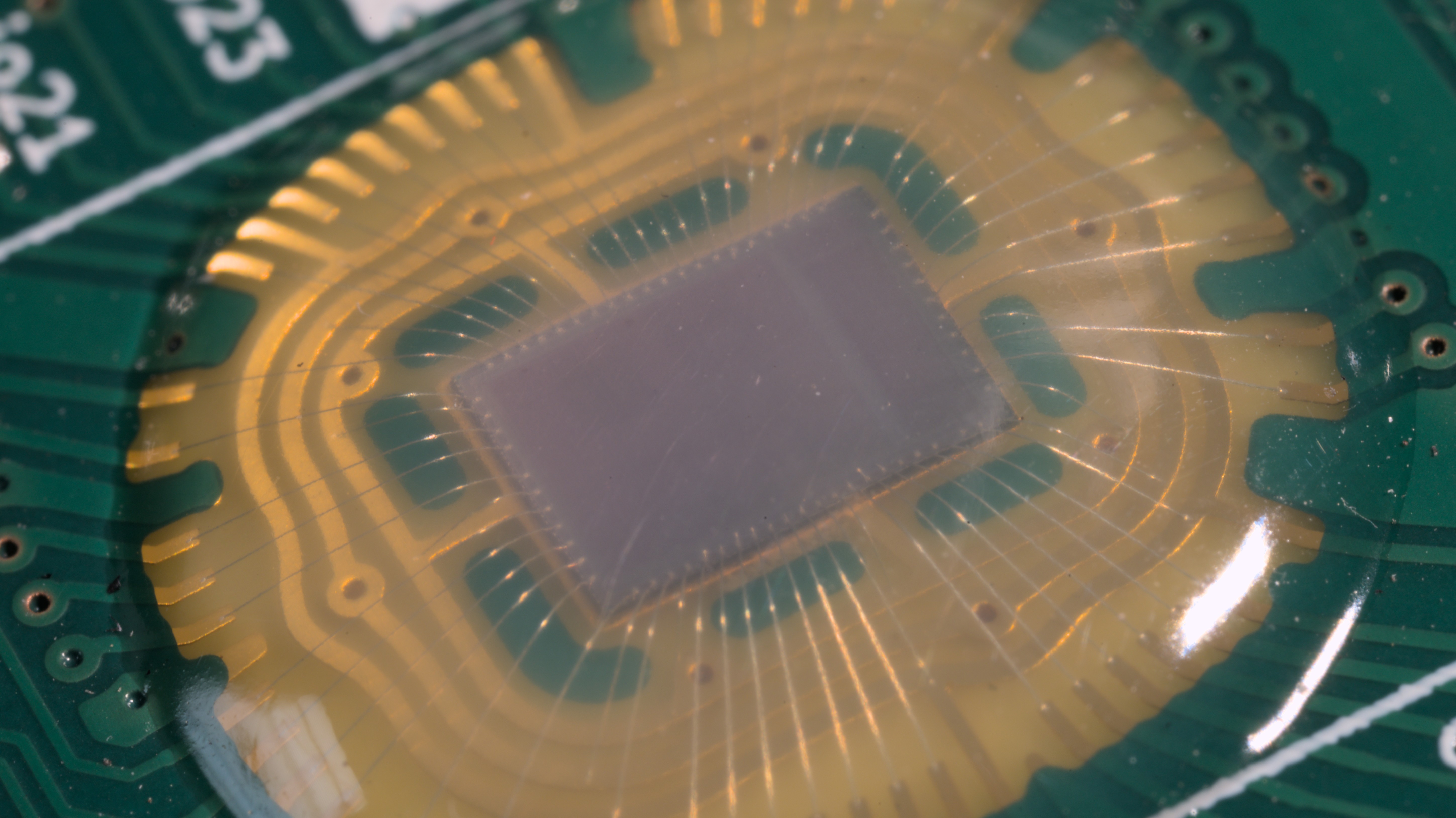

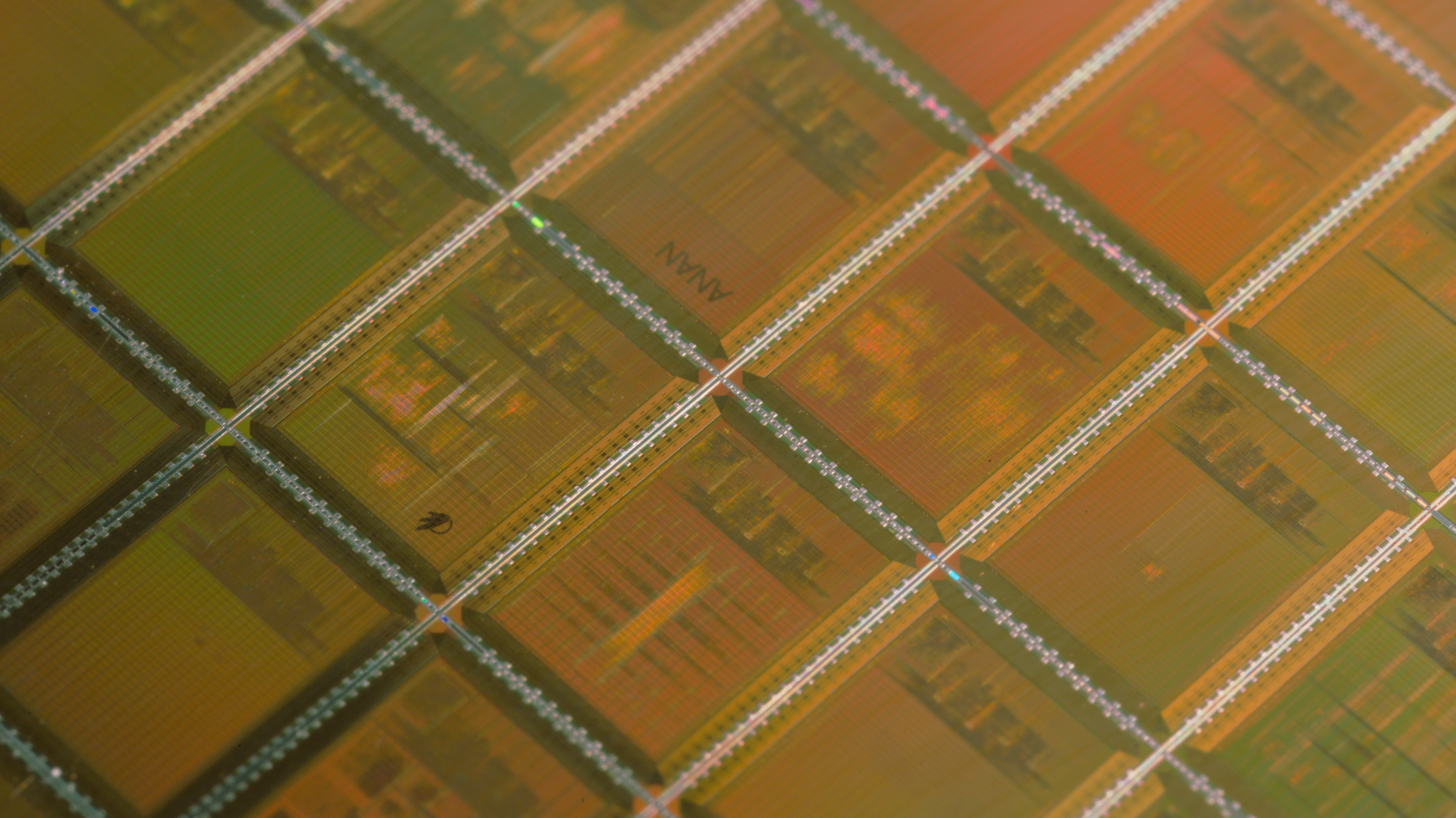

Take home a complete 200mm wafer with your design alongside other Run 2 projects.

Requires slot purchase

Add to Order

3 Sizes

1×1, 0.5×1 half-width, 1×0.5 half-height

5 Layers

Full routing capability

1,000 dies

Per manufacturing slot

MIM & MOS

Metal-insulator-metal and MOS capacitors available

Poly & High-Res

Multiple resistor types

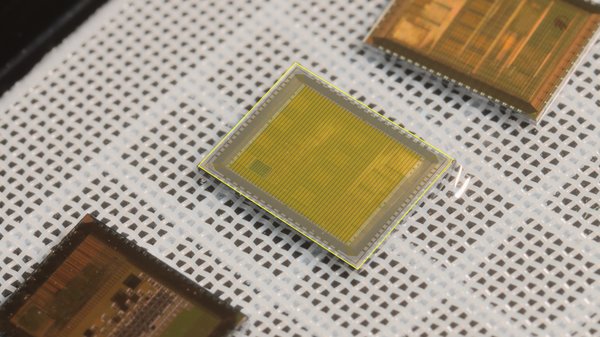

Silicon currently in fabrication — expected delivery late April 2026

1×1 slot

1×1 slot

1×1 slot

1×1 slot

1×1 slot

1×1 slot

1×1 slot

1×1 slot

1×1 slot

1×1 slot

Hard upper bounds — if you packed cells edge-to-edge with zero routing overhead

Flip-Flop (FF_1)

per mm² theoretical max

Buffer (BUF_4)

per mm² theoretical max

3-input AND (AND3_2)

per mm² theoretical max

Typical Range

logic cells/mm² for most digital designs

across 24 designs

| Design | Library | Core SC/mm² | % of max | Logic Cells | SRAM |

|---|---|---|---|---|---|

| Cloneless1 | 7t-5V | 22k | 44% | 316k | 0 |

| Tiny Tapeout (52 sub-designs) | mixed | 14k | 29% | 204k | 0 |

| FABulous FPGA | 7t-5V | 14k | 29% | 204k | 12 |

| Chess Move Gen. | 9t-5V | 10k | 25% | 145k | 0 |

| FazyRV Hachure | 7t-5V | 7k | 14% | 101k | 40 |

| KianV RISC-V | 9t-5V | 6k | 16% | 89k | 42 |

| Racquet 23-core | 7t-5V | 5k | 11% | 78k | 46 |

Data from the Run 1 Density Report. Logic cell counts exclude infrastructure cells (fillers, taps, antenna diodes). “% of max” compares against buf theoretical max for each library (50k for 7-track, 40k for 9-track).

| Cell Type | 1×1 Slot |

New! 0.5×1 Slot |

New! 1×0.5 Slot |

|---|---|---|---|

| Flip-Flop (FF_1) | ~185,014 | ~63,867 | ~71,886 |

| Buffer (BUF_4) | ~393,156 | ~135,718 | ~152,759 |

| 3-input AND (AND3_2) | ~508,790 | ~175,635 | ~197,688 |

Theoretical maximums with zero routing overhead. Run 1 designs typically achieved 10–44% of these values.

| SRAM Type | Voltage | 1×1 Slot | 0.5×1 Slot | 1×0.5 Slot |

|---|---|---|---|---|

| GF 5V sram512x8 | 5V | 40 kilobytes (80 blocks) | 20 kilobytes (40 blocks) | 20 kilobytes (40 blocks) |

| GF 5V sram256x8 | 5V | 28 kilobytes (112 blocks) | 14 kilobytes (56 blocks) | 14 kilobytes (56 blocks) |

| 3.3V sram1024x8 | 3.3V | 108 kilobytes (108 blocks) | 54 kilobytes (54 blocks) | 48 kilobytes (48 blocks) |

| 3.3V sram512x8 | 3.3V | 90 kilobytes (180 blocks) | 45 kilobytes (90 blocks) | 42 kilobytes (84 blocks) |

| 3.3V sram256x8 | 3.3V | 66 kilobytes (264 blocks) | 33 kilobytes (132 blocks) | 33 kilobytes (132 blocks) |

Block counts use die area minus seal ring (26µm each side). Run 1’s most SRAM-heavy design (RISCBoy-180) used 60 blocks in a full slot.

Theoretical numbers use core area (with default pad ring). Using your own pad ring or no pad ring increases available area.

Real designs achieve 10–44% of theoretical max due to routing overhead, infrastructure cells (~75% of instances), power planning, and clock distribution.

3.3V SRAM blocks from Tim Edwards and Tholin, introduced in Run 1.

Full analysis: Run 1 Standard Cell & SRAM Density Report.